Version 1.10 - January 2022

syn1588® Timestamping of User Defined Packets

# Abstract

The timestamping unit of the syn1588<sup>®</sup> Clock\_M IP Core used in the syn1588<sup>®</sup> PCIe NIC allows detecting two independent classes of Ethernet packets in both receive and transmit direction respectively. One packet class in each direction is used for detecting PTP packets and thus used by the syn1588<sup>®</sup> PTP Stack. The second timestamping unit may be used by the application software to detect an arbitrary class of Ethernet packets in each direction and draw a timestamp upon transmission or reception of a packet meeting the user defined filter condition.

This application note briefly outlines the required actions in the user software. A simple example is presented that may be extended to meet specific application requirements.

# Introduction

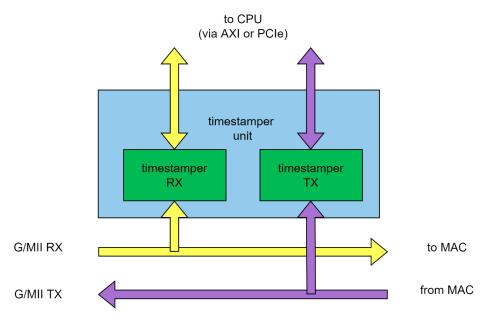

The timestamping unit available in the syn1588<sup>®</sup> PCIe NIC allows detecting of two independent classes of Ethernet packets both for receive and transmit direction. The following figures show the basic principle of these two units both being attached to the G/MII interface as pure listening devices. Consequently, these timestamping units act as passive observers on the G/MII interface without altering the data transferred in either direction.

Figure 1. G/MII timestamping units in the syn1588<sup>®</sup> PCIe NICs

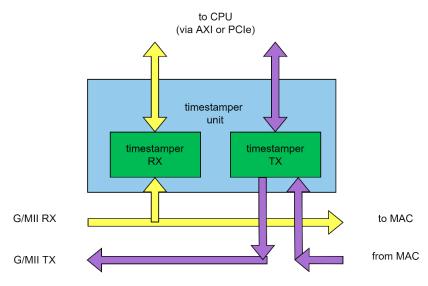

For two-step operation both timestamp units passively attach to the Media Dependent Bus interface of the MAC-to-PHY connection. For 1-step operation the transmit bus is fed through the timestamping units since the timestamp has to be inserted on-the-fly.

Figure 2. G/MII timestamping units in 1-step mode

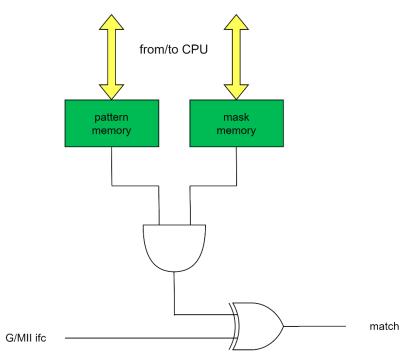

The following figure shows the basic element of the timestamping unit: the timestamping comparator. Two of these comparators are contained in one timestamping unit. Two timestamping units comprising four timestamping comparators are available in the syn1588<sup>®</sup> PCIe NIC.

Figure 3. Basic timestamping comparator

The timestamping comparator will check up to 128 bytes of every Ethernet packet. The compare process starts with the first byte following the SFD (start-of-frame-delimiter). For every bit of the packet the user may define an expected value and a mask value. For every bit that is set to 1 in the mask memory the value of the bit in the packet is compared against the value of the respective bit in the pattern memory.

The timestamping comparator produces a match, if all active data bits in the pattern memory (i.e the bits with the corresponding mask bits set to 1) match the respective bits in the packet. In this case the timestamp of the respective packet which has been drawn previously (i.e. at SFD) is copied into a FIFO buffer memory. To allow the user application to distinguish these packets from other Ethernet traffic additional packet data can be copied into the buffer memory together with the time stamp.

A control register is attached to every timestamping comparator. providing the means to enable the timestamping comparator as well as to define the overall length of the filter (i.e. the number of bits to be analyzed starting from the SFD) and two separate data sections to be copied into the buffer memory The latter are defined via two independent offset and length values.

## **Timestamp Unit Control Register**

Four distinct Timestamp Unit control registers are available; one for each timestamping comparator. The following table shows the contents of these Timestamp Unit control register.

| Bit(s)      | Description                                                                                                                                                                                               |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NBYTES[7:0] | Number of bytes in the packet to compare against the pattern & mask memory. If NBYTES is set to 0 the time stamping unit is disabled. If NBYTES is larger than the total packet length no match is found. |  |

|             | If the first NBYTES of the packet match against the pattern & mask RAM the packet is matched and the timestamp as well as the extracted data is written to the FIFO.                                      |  |

| LEN1[11:8]  | Length in number of bytes to extract from the packet starting at OFF1 to be stored into the time stamping unit FIFO.<br>Note: (LEN1 + LEN2) mod 4 = 0                                                     |  |

| LEN2[15:12] | Length in number of bytes to extract from the packet starting at OFF2 to be stored into the time stamping unit FIFO.<br>Note: (LEN1 + LEN2) mod 4 = 0                                                     |  |

| OFF1[23:16] | Offset value for the first data section to extract from the packet if a match has been found. The values is counted in multiples of bytes starting with the first byte after the SOF octet                |  |

| OFF2[31:24] | Offset value for the second data section to extract from the packet if a match has been found. The values is counted in multiples of bytes starting with the first byte after the SOF octet               |  |

#### Table 1 Timestamp Unit Control Register - register bits

The following table lists the address of these control registers. Note that these are the local address of the syn1588<sup>®</sup> PCIe NIC.

| Address | Description                                    |

|---------|------------------------------------------------|

| 0x1214  | MII Timestamper #0 Receive – control register  |

| 0x1208  | MII Timestamper #0 Transmit – control register |

| 0x120c  | MII Timestamper #1 Receive – control register  |

| 0x1210  | MII Timestamper #1 Transmit – control register |

#### Table 2 Address map of the Timestamp Unit Control Registers

For every timestamping unit a separate pattern and mask memory defining the comparator condition is implemented. To simplify the implementation and access the pattern and mask data are combined into one memory. with 128 entries; every entry containing one mask and one pattern byte. The even byte

of the pattern and mask memory hold the pattern data while the mask value is stored at the odd byte location

The following table lists the base addresses of these pattern & mask memories.

| Address | Description                                         |

|---------|-----------------------------------------------------|

| 0x1400  | MII Timestamper #0 Receive – pattern & mask memory  |

| 0x1600  | MII Timestamper #0 Transmit – pattern & mask memory |

| 0x1800  | MII Timestamper #1 Receive – pattern & mask memory  |

| 0x1a00  | MII Timestamper #1 Transmit – pattern & mask memory |

Table 3 Addresses map of the Timestamp Unit pattern and mask memories

Finally, for every timestamping comparator a separate timestamping FIFO is available. Whenever the respective comparator detects a packet matching its preset condition the packet's timestamp value as well as optional data extracted from the packet are stored in this timestamping FIFO. Additionally, an interrupt is generated informing the user application or the syn1588<sup>®</sup> PTP Stack that there is new data available.

| Address | Description                      |

|---------|----------------------------------|

| 0x1010  | MII Timestamper #0 Receive FIFO  |

| 0x1018  | MII Timestamper #0 Transmit FIFO |

| 0x101C  | MII Timestamper #1 Receive FIFO  |

| 0x1020  | MII Timestamper #1 Transmit FIFO |

Table 4 Addresses of the Timestamp Unit FIFOs

### Version 1.10 - January 2022

Finally there is a status register for every RX/TX timestamp FIFO pair available.

| Bit(s)             | Description                                        |

|--------------------|----------------------------------------------------|

| RX FIFO EMPTY[0]   | a '1' flags that the RX timestamp FIFO is empty    |

| RX FIFO FULL[1]    | a '1' flags that the RX timestamp FIFO is full     |

| RX FIFO CNT[9:2]   | number of words available in the RX timestamp FIFO |

| RESERVED[15:10]    | reserved                                           |

| TX FIFO EMPTY[16]  | a '1' flags that the TX timestamp FIFO is empty    |

| TX FIFO FULL[17]   | a '1' flags that the TX timestamp FIFO is full     |

| TX FIFO CNT[25:18] | number of words available in the TX timestamp FIFO |

| RESERVED[31:26]    | Reserved                                           |

#### Table 5 Timestamp Unit FIFO Status Register – register bits

| Address | Description                    |

|---------|--------------------------------|

| 0x1030  | MII Timestamper #0 FIFO Status |

| 0x1034  | MII Timestamper #1 FIFO Status |

Table 6 Address map of the Timestamp Unit FIFO Status Register

## **User Timestamping Demo Application**

A simple example is available, which shows how to setup the timestamping unit for a given class of Ethernet traffic. The example source-code may be found on the wooden Oregano Systems' USB stick containing the syn1588<sup>®</sup> Live System in the folder /sw/api/.

This folder contains a .zip file which in order contains the syn1588<sup>®</sup> API example source code and build environment.

The source code is written for Linux and for Windows. For the compilation on Linux OS, GNU-make is used together with the g++ compiler and for Windows OS the Microsoft Visual Studio compiler is used. If you require further information, please contact the Oregano Systems support.

Version 1.10 - January 2022

|                                                    |                    | Copyright © 2022                                                                                                                                                                                                                                                                                |

|----------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | C                  | Oregano Systems – Design & Consulting GmbH                                                                                                                                                                                                                                                      |

| Oregano                                            | Systems            | ALL RIGHTS RESERVED.                                                                                                                                                                                                                                                                            |

| Franzosengraben 8<br>A-1030 Vienna                 | A Meinberg Company | Oregano Systems does not assume any liability arising out of the application or use of<br>any product described or shown herein nor does it convey any license under its patents,<br>copyrights, or any rights of others.                                                                       |

| Austria<br>http://oregano.at<br>contact@oregano.at |                    | Licenses or any other rights such as, but not limited to, patents, utility models, trademarks or tradenames, are neither granted nor conveyed by this document, nor does this document constitute any obligation of the disclosing party to grant or convey such rights to the receiving party. |

|                                                    |                    | Oregano Systems reserves the right to make changes, at any time without notice, in order to improve reliability, function or design. Oregano Systems will not assume responsibility for the use of any circuitry described herein.                                                              |

|                                                    |                    | All trademarks used in this document are the property of their respective owners.                                                                                                                                                                                                               |