# syn1588<sup>®</sup> PTP Stack

### **Brief Data Sheet**

Version 1.6 – December 2020

#### **Features**

- IEEE 1588-2008 compliant

- IEEE 1588-2019 support added step-by-step

- hardware timestamping support with syn1588<sup>®</sup> technology

- SO\_TIMESTAMPING support

- Full Master and Slave capability

- Support for E2E, P2P and pure clock syntonization

- One-step (syn1588<sup>®</sup> hardware) and two-step clock support

- IPv4, IPv6, and Layer-2 (Linux only) transport

- IEEE 1588 Management support

- Linux PHC support for operation

with compatible NICs

- Unicast operation

- Hybrid Mode (multicast / unicast)

- Full Boundary Clock operation

- NetSync Monitor supported

#### Profiles

- Broadcasting

- o SMPTE ST2059-2

- o AES-67

- Default profile

- o IEEE 1588-2008, Annex J3

- Enterprise profile

- Power Profiles

- o IEEE C37.238-2014

- o IEEE C37.238-2017

- Telecom Profiles

- o T.REC-G.8265.1

- o T.REC-G.8275.1

- o T.REC-G.8275.2

- IEEE 802.1AS

### Options

- APIs for controlling and monitoring

- External tools for synchronizing additional clocks

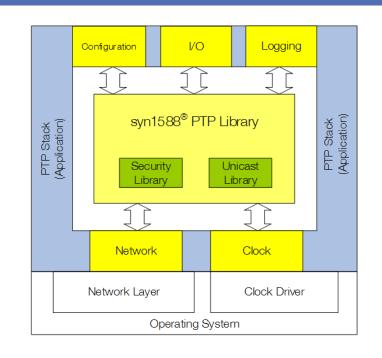

syn1588® PTP Stack block diagram

The syn1588® PTP Stack is a lightweight Precision Time Protocol stack fully compliant to the IEEE 1588-2008 & IEEE1588-2019 standard enabling highly accurate clock synchronization in local area networks. It is designed using strictly encapsulated software а structure combined with distinct interfaces between the various modules of the syn1588® PTP Stack.

Due to its extensive PTP profile support the syn1588<sup>®</sup> PTP Stack is ideally suited for a variety of applications ranging from the broadcasting industry to financial service providers. It may act as a Power Profile node as well as a Telecom Grandmaster Clock, depending on the requirements of the target system. For multiport devices the syn1588<sup>®</sup> PTP Stack offers full Boundary Clock support.

The syn1588<sup>®</sup> PTP Stack supports Time Sensitive Networks (TSN) as well offering full IEEE 802.1AS support both for bridges and end nodes.

The syn1588<sup>®</sup> PTP Stack is written as a user space application capable of operating on a standard PC as well as any microcontroller. Windows and Linux operating systems are natively supported. Originally, it has been designed to be used with an Oregano Systems' high-accuracy PTP network interface card (syn1588<sup>®</sup> PCle NIC). Due to its highly modular architecture, porting of the syn1588<sup>®</sup> PTP Stack to other platforms is an effortless task. On Linux the socket based hardware time stamping option (SO\_TIMESTAMPING) is supported. Merely the interfaces to and from the PTP library have to be adapted accordingly to build a syn1588<sup>®</sup> PTP Stack capable of communicating with any other 3<sup>rd</sup> party PTP hardware.

All timing critical operations like timestamping are handled in hardware when using the Oregano Systems syn1588<sup>®</sup> hardware or 3<sup>rd</sup> party network interface cards with Linux PTP Hardware Clock (PHC) support (e.g. Intel i210 NIC family). Further-more, the syn1588<sup>®</sup> PTP Stack can operate without any dedicated IEEE 1588 hardware support as well. In this mode the system clock is used as a time reference.

The syn1588<sup>®</sup> PTP Stack is a well proven, easy-to-use PTP solution and has been tested successfully for compatibility with various other implementations of other vendors e.g. at every ISPCS plugfest since 2007 or at SMPTE interops. For further details and information like resource utilization, custom solutions as well as optional features, please contact Oregano Systems.

# syn1588® PTP Stack

**Brief Data Sheet**

## Version 1.6 – December 2020

| Technical Specifications        |                                                                                                  |

|---------------------------------|--------------------------------------------------------------------------------------------------|

| Standards & PTP Profile Support | IEEE 1588-2008, IEEE 1588-2019                                                                   |

|                                 | IEEE C37.238-2011, IEEE C37.238-2014                                                             |

|                                 |                                                                                                  |

|                                 | ITU-T G.8265.1/Y.1365.1 (10/2010), ITU-T G.8275.1, ITU-T G.8275.2                                |

|                                 | SMPTE ST2059-2-2015                                                                              |

|                                 | AES-67-2015,                                                                                     |

| Natively supported hardware     | Oregano Systems' syn1588 <sup>®</sup> PCIe NIC                                                   |

|                                 | Oregano Systems' syn1588 <sup>®</sup> Dual NIC                                                   |

|                                 | Oregano Systems' syn1588 <sup>®</sup> VIP                                                        |

|                                 | Oregano Systems' syn1588 <sup>®</sup> Clock_M IP core family                                     |

|                                 | Network Interface Cards supporting the Linux PHC interface and the Linux SO_TIMESTAMPING feature |

|                                 | Miscellaneous Network Interface Cards (software timestamping only)                               |

| Operating system support        | Linux (32/64 bit)                                                                                |

|                                 | Microsoft Windows Server 2003, 2008, 2012, 2016, 2019 (32/64 bit)                                |

|                                 | Microsoft Windows 7 (32/64 bit)                                                                  |

|                                 | Microsoft Windows 10 (32/64 bit)                                                                 |

|                                                                           |                    | Copyright © 2020                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oregano                                                                   | Systems            | Oregano Systems – Design & Consulting GmbH<br>ALL RIGHTS RESERVED.                                                                                                                                                                                                                                       |

| A Meinberg Co                                                             | A Meinberg Company | Oregano Systems does not assume any liability arising out of the application<br>or use of any product described or shown herein nor does it convey any<br>license under its patents, copyrights, or any rights of others.                                                                                |

| Franzosengraben 8<br>A-1030 Vienna<br>Austria<br><u>http://oregano.at</u> |                    | Licenses or any other rights such as, but not limited to, patents, utility<br>models, trademarks or tradenames, are neither granted nor conveyed by<br>this document, nor does this document constitute any obligation of the<br>disclosing party to grant or convey such rights to the receiving party. |

| contact@oregano.at                                                        |                    | Oregano Systems reserves the right to make changes, at any time without<br>notice, in order to improve reliability, function or design. Oregano Systems<br>will not assume responsibility for the use of any circuitry described herein.                                                                 |

|                                                                           |                    | All trademarks used in this document are the property of their respective owners.                                                                                                                                                                                                                        |